- 您现在的位置:买卖IC网 > Sheet目录2098 > MK2069-01GILFTR (IDT, Integrated Device Technology Inc)IC VCXO CLK SYNCHRONIZER 56TSSOP

MK2069-01

VCXO-BASED LINE CARD CLOCK SYNCHRONIZER

VCXO AND SYNTHESIZER

IDT VCXO-BASED LINE CARD CLOCK SYNCHRONIZER

9

MK2069-01

REV K 051310

Notes on Setting the RV, FV and SV Divider

Values

As shown in the loop bandwidth and damping factor

equations on page 6, or by using the filter response software

available from IDT, increasing FV or SV decreases both

bandwidth and damping factor. Many applications require

that SV = 1. In these cases, one way to decrease loop

bandwidth is to increase the value of FV, which is

accompanied by an increase in the value of RV to maintain

the same PLL frequency multiplication ratio.

However, the phase detector frequency, FPD, also needs to

be considered. FPD is equal to the input frequency divided

by the value of the RV divider. FPD should be typically at

least 20x the loop bandwidth to prevent loop modulation

(phase noise) by the phase detector frequency. The phase

detector jitter tolerance limit (use 0.4UI) and input phase

noise frequency aliasing should be considerations as well.

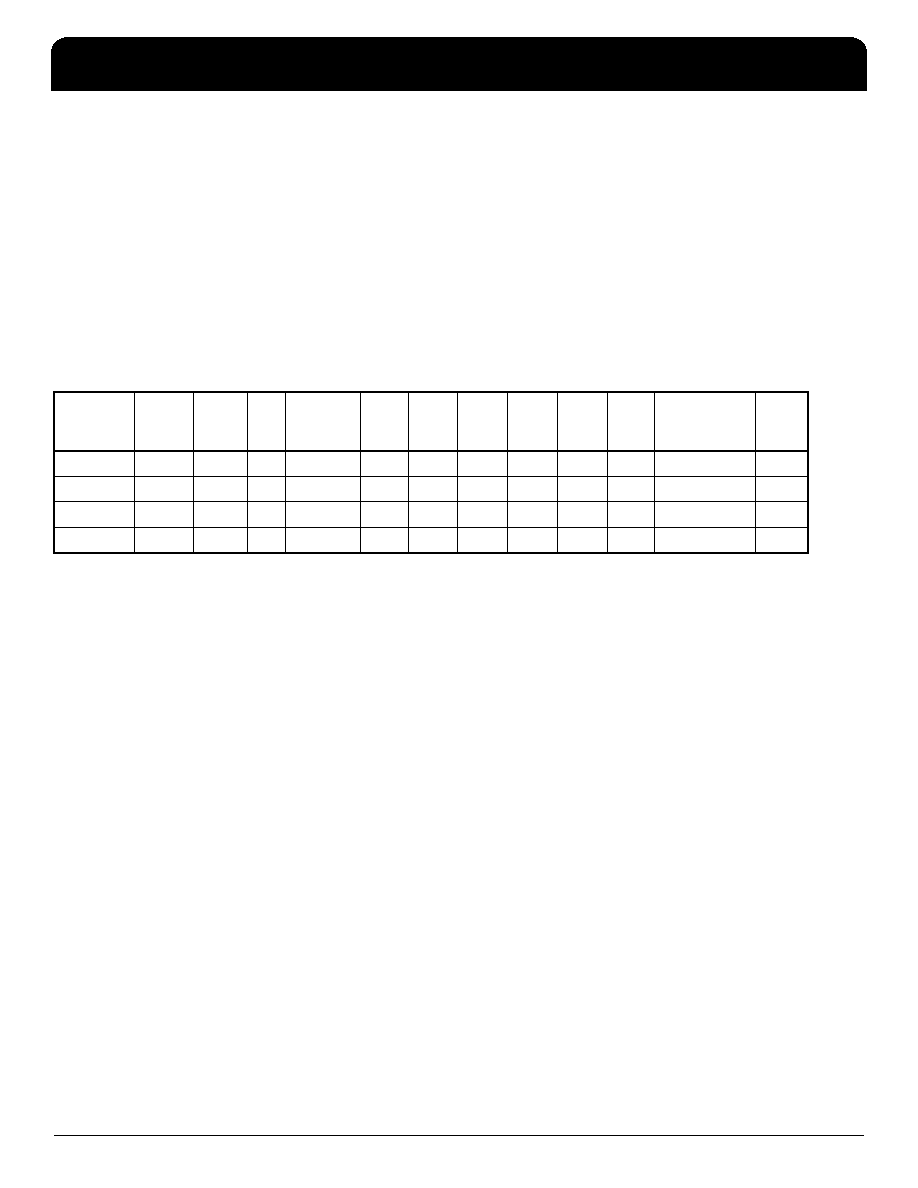

Example Loop Filter Component Value

Notes:

1) This filter configuration assures a passband ripple compliant with Bellcore GR-1244 to satisfy wander transfer

requirements (<0.2 dB ripple is required) of a network node. It can be used following a system synchronizer such as

the MT9045 to provide clock jitter attenuation while maintaining Stratum 3 compliance. A 155.52 MHz TCLK output

generated with the VCXO PLL configuration will be OC-3 and OC-12 timing jitter compliant.

2) This is a reduced cost and size variant of the above filter, due to the decreased size of CS. It is useful when GR-1244

compliance is not needed, such as in a network access application.

3) This configuration is used to generate a DS3 clock of 44.768 MHz at the TCLK output. This configuration is GR-1244

compliant.

4) The MK2069-02 or MK2069-04 may be more suitable for this application since the VCXO feedback divider can be

increased (>128), enabling a lower bandwidth for improved jitter attenuation.

Loop Filter Capacitor Type

Loop filters must use specific types of capacitors.

Recommendations for these capacitors can be found at

www.idt.com/?app=calculators&source=support_menu.

Input MUX

The MK2069-01 incorporates an input clock multiplexer or

‘mux’ that allows selection between one of three alternate

reference inputs supplied to the device. The mux input

selection pins are asynchronous and non-latched. Please

refer to the Input MUX Selection Table on page 2. Note that

inputs ICLK0 and ICLK1 are 5V tolerant, whereas ICLK2 is

not.

Input Phase Compensation Circuit

The VCXO PLL includes a special input clock phase

compensation circuit. It is used when selecting a new

reference input that has a clock phase differing from the

Input

Clock

Xtal

Freq

(MHz)

VCLK

(MHz)

RV

Div

FV

Div

SV

Div

RSET

RS

CS

CP

Loop

BW

(-3dB)

Loop

Damp.

Passband

Peaking

Note

8 kHz

19.44

1

2430

1

1 M

Ω 560 kΩ 1 μF 4.7 nF 22 Hz

4.0

0.15dB at 1Hz

1

8 kHz

19.44

1

2430

1

1 M

Ω 560 kΩ 0.1 μF 4.7 nF 27 Hz

1.4

1.2dB at 6Hz

2

8 kHz

22.368

1

2796

1

1 M

Ω 680 kΩ 1 μF 4.7 nF 20 Hz

4.5

0.12dB at 1Hz

3

19.44 MHz

19.44

128

1

1 M

Ω 27 kΩ

1

μF

47 nF

25 Hz

0.85

1.8dB at 8Hz

4

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MK2069-04GILFTR

IC VCXO CLK TRANSLATOR 56-TSSOP

MK2302S-01LFTR

IC MULTIPLIER/ZD BUFFER 8-SOIC

MK2304S-2LF

IC PLL ZD BUFFER LO SKEW 8-SOIC

MK2703SILF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2704SLF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2716SLFTR

IC CLK SYNTHESIZER HDTV 8-SOIC

MK2732-06GLF

IC VCXO/MULTIPLIER 16-TSSOP

MK2745-21SLFTR

IC CLK SOURCE DVD/MPEG 16-SOIC

相关代理商/技术参数

MK2069-01GITR

功能描述:IC VCXO CLK SYNCHRONIZER 56TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

MK2069-03

制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Clock Translator with High Multiplication

MK2069-03GI

功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

MK2069-03GITR

功能描述:时钟发生器及支持产品 VCXO-BASED CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56

MK2069-04

制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Universal Clock Translator

MK2069-04GI

功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

MK2069-04GILF

功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56

MK2069-04GILFTR

功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56